2D-NANDの概要は、「NADフラッシュメモリ」の記事で説明しました。この記事では、「3D-NANDフラッシュメモリ」の構造や変遷について説明していきたいと思います。

3D-NANDフラッシュメモリの外観

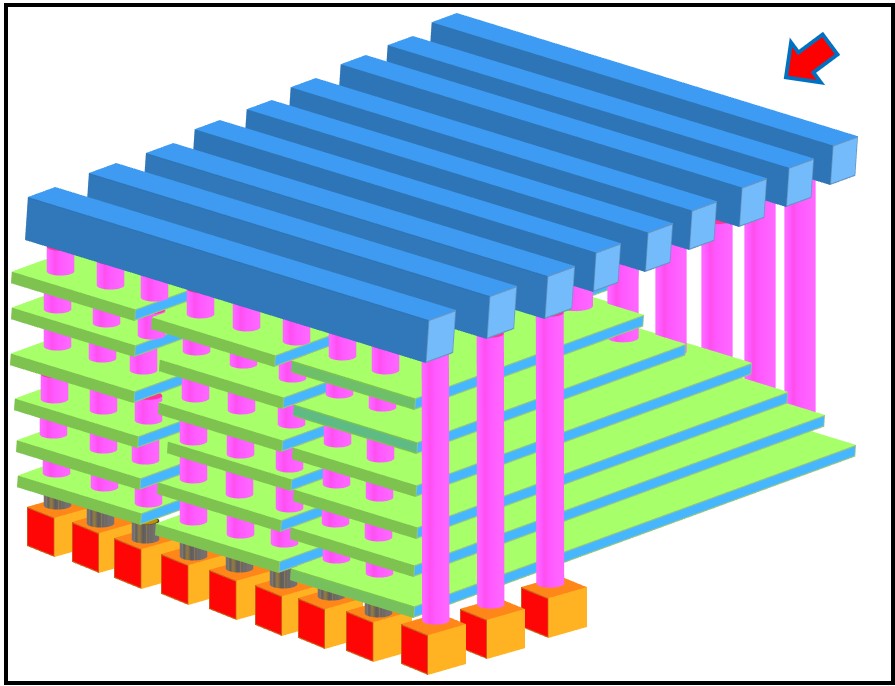

まずは、下図に3D-NANDフラッシュメモリの概要図を示します。このデバイスの構造は、少し複雑なので、矢印で示した方向からの図も掲載します。

上図で一番上の青い棒状のパーツがあると分かり難いと思いますので、このバーツの部分を半透明にしています。反対側から見ると、手前の部分が階段状になっていることが分かると思います。この階段状の構造にも意味があるのですが、それは後ほど説明していきたいと思います。

少し、イギリスのSIS本部ビルに形が似ていますね。正面から見ると、普通のビルっぽいんですが、テムズ川から見ると階段状になっているところがSIS本部ビルっぽい感じです。

3D-NANDフラッシュメモリの構造

・2D-NANDを90°立ててみると

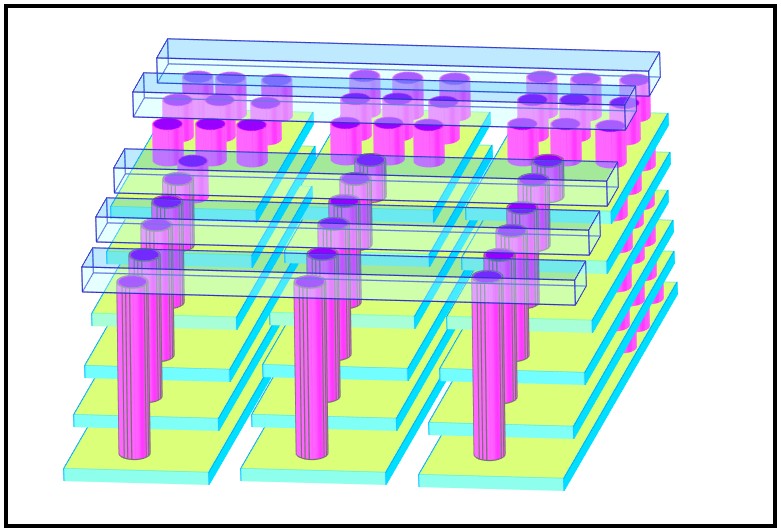

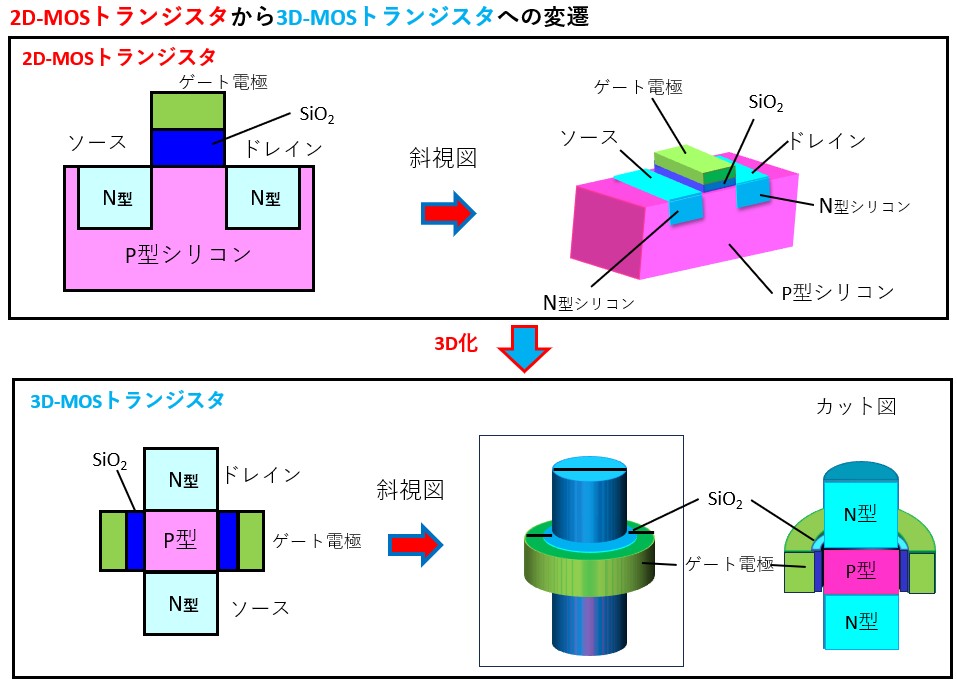

3D-NANDフラッシュメモリとは、その名前が示す通り、3次元構造をしています。しかし、基本的なメモリ機構は2D-NANDフラッシュメモリと同じになります。おさらいになりますが、2D-NANDフラッシュメモリの構造を下図に示します(詳細は、「NANDフラッシュメモリ」を参照して下さい)。

上記の2D-NANDフラッシュメモリを矢印の様に90°立たせた図を下図に示します。これだけでは、ただ横にあったものを縦にしただけです。ここで、フラッシュメモリの構造が2D-NANDフラッシュメモリから変化します。

・MOSトランジスタの3次元化

フラッシュメモリの説明の際に、まずNMOSトランジスタの説明から初めて、次にコントロールゲートとフローティングゲートを持つフラッシュメモリを説明しました。

同じように、通常のNMOSトランジスタから3D-MNOSトランジスタを考えて、2D-NANDフラッシュメモリから3D-NANDフラッシュメモリを説明していきたいと思います。

3D-NMOSトランジスタというのは、実際には存在いないようですが、説明の過程であった方が分かりやすいと思いますので、3D-NMOSトランジスタを仮想的ですが考えてみます。

下図の「3D化」以降の部分を見てもらえれば分かる通り、まず中心に円筒形のP型シリコンがあり、それを取り囲むようにドーナツ状のSiO2膜で取り囲んでいます。さらに、SiO2膜を取り囲むようにドーナツ状のゲート電極が形成されています。

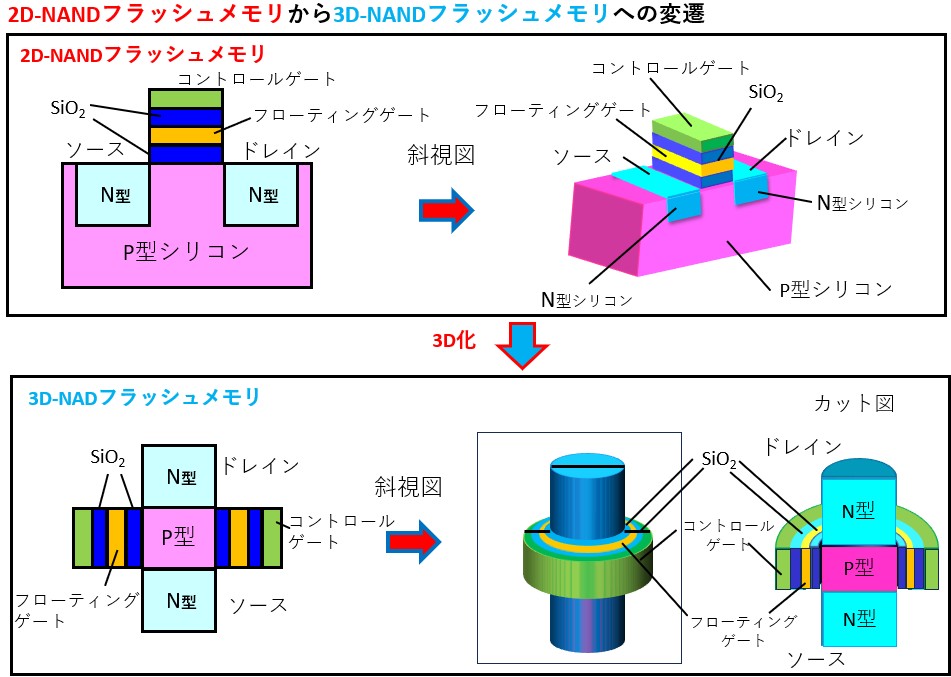

次に、2D-NANDフラッシュメモリから3D-NANDフラッシュメモリ変化を見てみましょう。

・2D-NANDフラッシュメモリから3D-NANDフラッシュメモリへの変遷

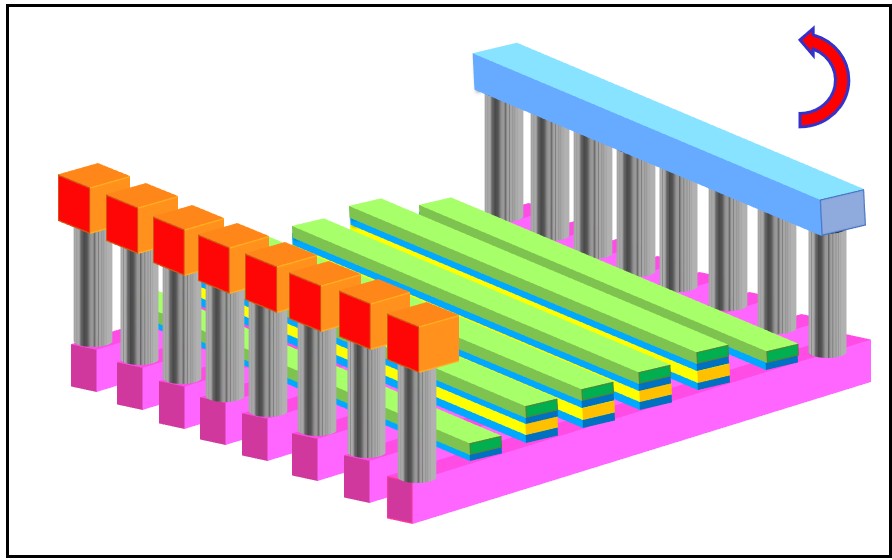

下図、上部は「2D-NANDフラッシュメモリ」の図です。従来の「2D-MOSトランジスタ」にはなかったフローティングゲートが付け加わっているのが特徴です。

同じように、「2D-NANDフラッシュメモリ」から「3D-NANDフラッシュメモリ」への進化を考えると以下のようになります。

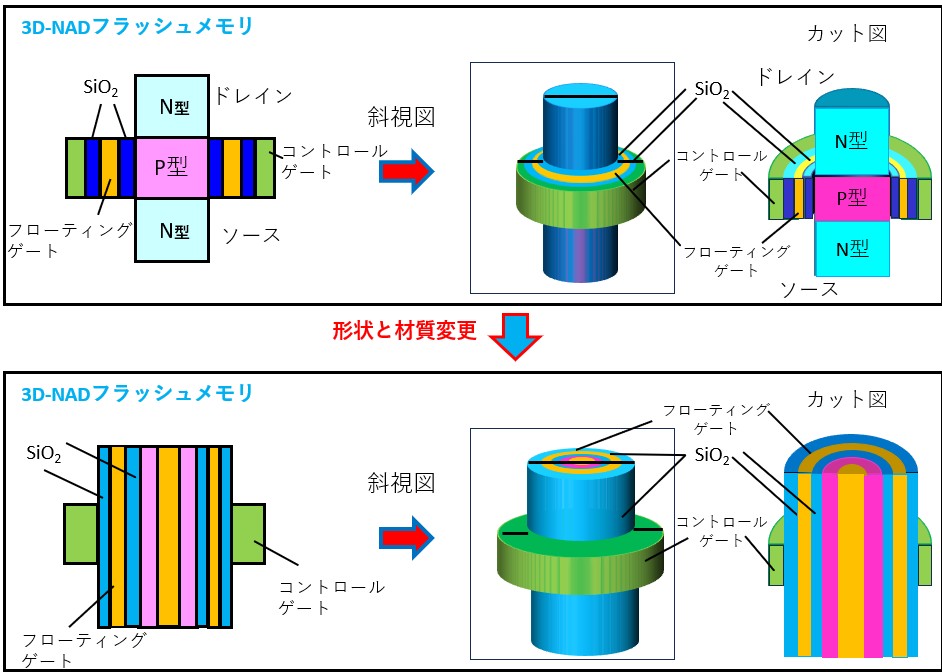

最初の開発当初の構造では、上記のような構造だったようですが、その後開発が進むに従って材質や構造が変わってきます。

現在の「3D-NANDフラッシュメモリ」は真ん中にSiO2の芯が入り、SiO2絶縁膜やフローティングゲートも上下に伸びる構造になっているようです。

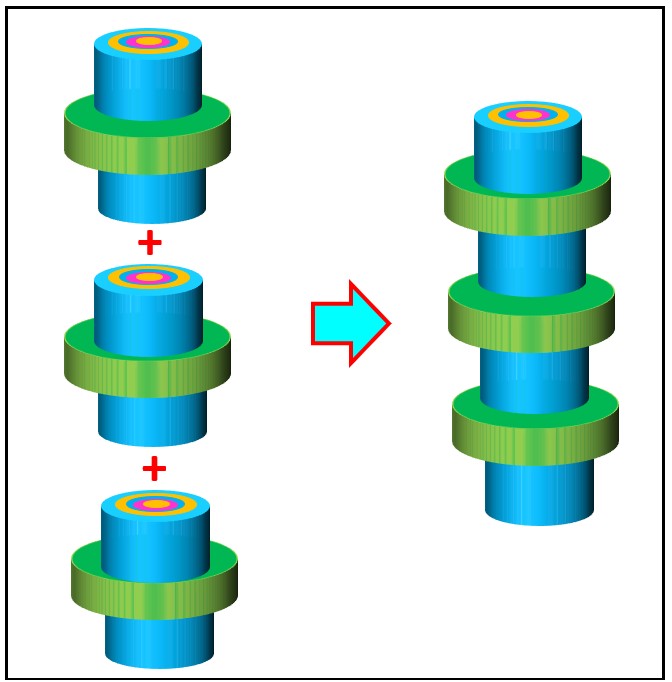

ここまでが、1セルの構造です。「3D-NANDフラッシュメモリ」は「2D-NANDフラッシュメモリ」のように、「ソース」と「ドレイン」をくっつけます。それを下図に示します。

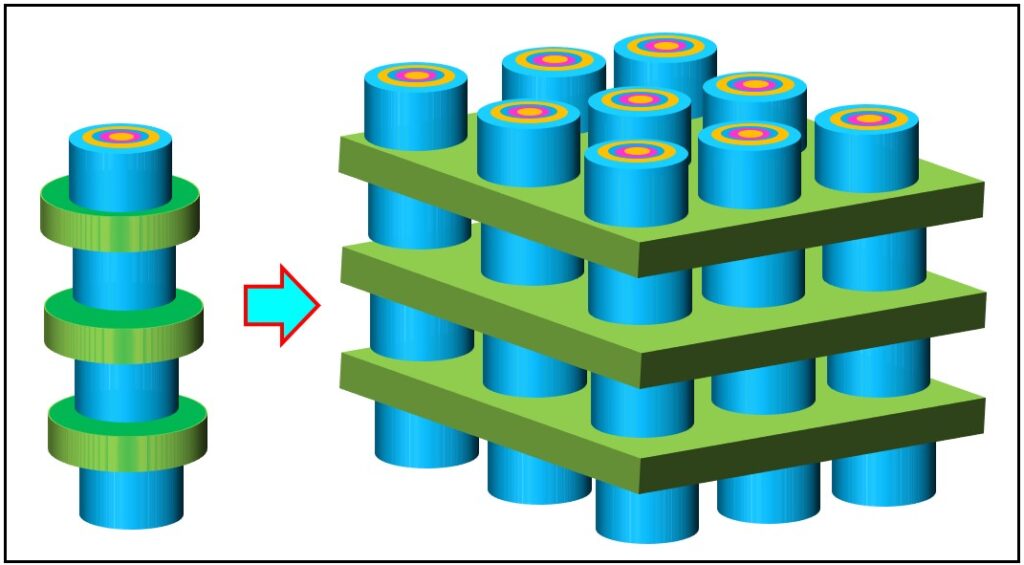

今度は、この構造を縦横に広げていきます。このようにNANDメモリセルを縦横に拡張していくことで、「3D-NANDメモリ」セルデバイスの面積当たり・体積当たりの集積度は増して行きます。

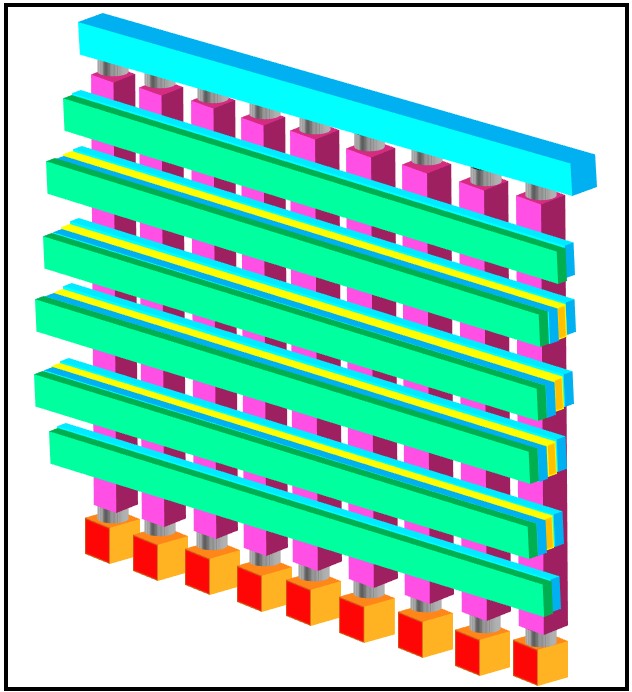

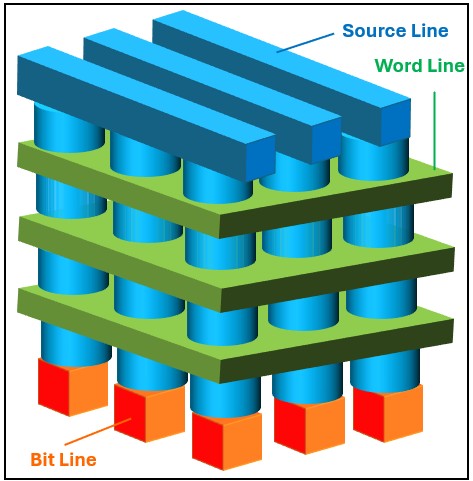

段々と完成形に近づいてきました。今度は、このデバイスの上段にソースラインを追加し、下端にビットライン選択用の端子を追加します。

これで、ビットラインが選択できることになりました。「NANDフラッシュメモリ」の記事でも書きましたが、メモリ情報の読み出しをする場合は、ビットラインをOnし、読み出したいメモリセルのあるワードラインを+5Vに印加し、その他のメモリセルのワードラインを+10Vに印加してやる必要があります。

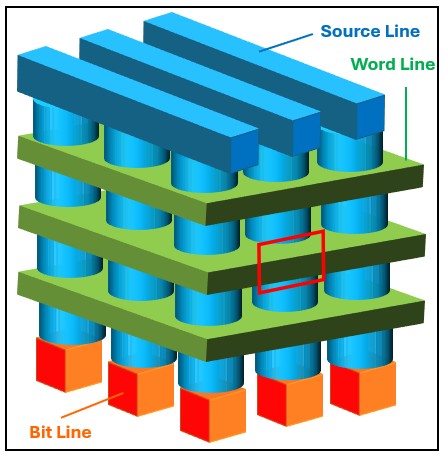

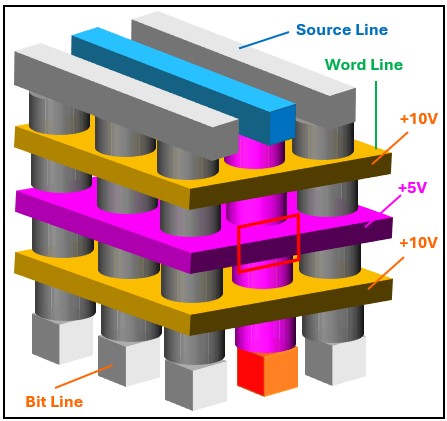

例えば下図の赤線で囲ったメモリセルの状態を確認したい場合があるとします。2D-NANDフラッシュメモリの記事でも解説しましたが、Word Lineが+5Vの時は、フローティングゲートに電子が入っているかどうかで、MOSトランジスタの動作が変わってきます。

Word Lineが+10Vの時は、フローティングゲートに電子が入っているかどうかに関わらず、MOSトランジスタはOnになります。

その場合は、次の様になります。このように各電極に電圧をかけ、その結果配線に通電があった場合には、フローティングゲートに電荷が入っていなかったことが明らかになり、メモリ状態は、’0’となり、配線に通電がなかった場合には、フローティングゲートに電荷が入っていたことが明らかになり、メモリ状態は、’1’となります。

コメント