最近、半導体関連のニュースを聞くことがあります。その中で、配線幅何nmという言葉がよく出てきます。その配線幅について、記事を書いてみようと思います。

テクノロジー・ノード(デザイン・ルール)

この配線幅とは、「テクノロジー・ノード」とも「デザイン・ルール」とも呼ばれています。「テクノロジー・ノード」は「DRAM/MPU」と「NANDフラッシュメモリ」で定義がことなっているのですが、ここでは「DRAM/MPU」の例で説明していきたいと思います。

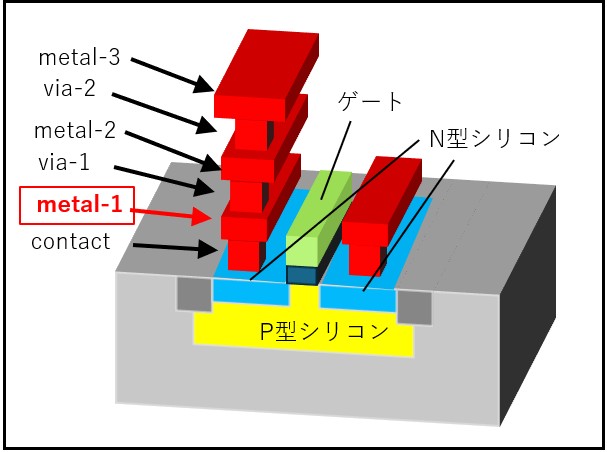

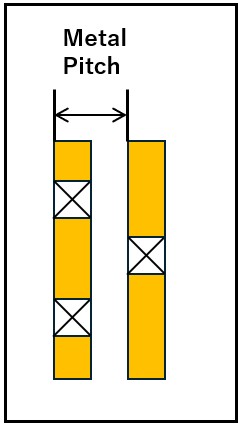

端的にいうと、図中の「metal-1」と赤字で書いてある部分の配線幅になります。この部分を、「M1ステップのハーフピッチ」といいます。

これは、ITRS(International Technology Roadmap for Semiconductor:国際半導体技術ロードマップ委員会)が定義した寸法になります。

この「metal-1」工程が、微細化の中で一番難しい工程らしくて、この配線幅が半導体デバイスの微細化の指標として使われていたらしいです。

現在のテクノロジー・ノード

しかし、最近ではテクノロジー・ノードが上記のような物理的な部分配線とは異なる意味で使われることが多くなって来ているようです。

理由の1つに現在のMOSセル構造が、上記ITRSがテクノロジー・ノードを定義したした時と変化してしまったことが考えられます。

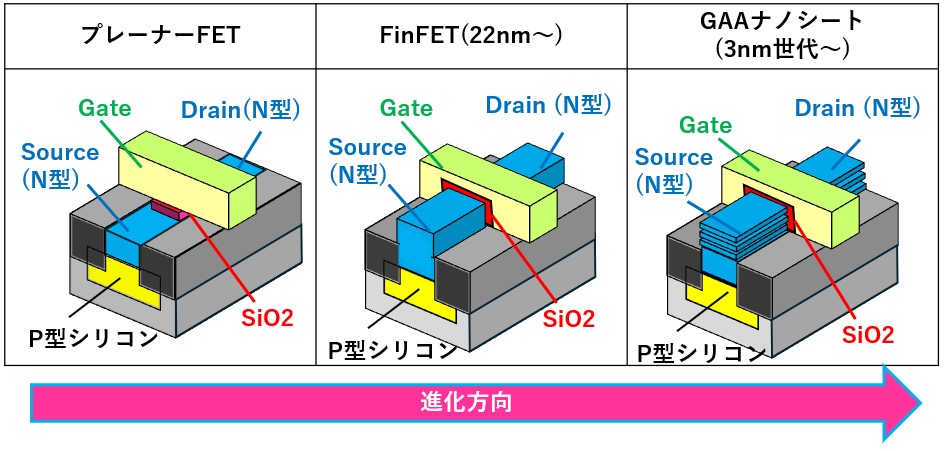

上記で記した、「M1ステップのハーフピッチ」は、下図で示した「プレーナーFET」構造時の時に定義されたものです。

その後、微細化が進んで、MOSセル構造は「FinFET」構造、さらには「GAA(Gate-All-Aroud)」構造に進化していきます。

「GAA」構造になってしまったMOSセルに「プレーナーFET」の時代に定義した、「テクノロジー・ノード」を当てはめるのは難しいからではないかと思われます。

コメント