今回の記事では、半導体デバイスの一つである、「NANDフラッシュメモリー」を取り上げようと思います。「半導体」の記事でも取り上げましたが、コンピュータ内部で使われる「半導体デバイス」には、大きく分けて「ロジックデバイス」と「メモリデバイス」があります。

その中で「NANDフラッシュメモリー」は「メモリデバイス」の一種類です。珍しく日本で発明された「半導体デバイス」で、近年市場規模が拡大しているデバイスです。

その原理は、「MOSトランジスタ」を応用したものです。「フラッシュメモリー」には、「NAND型」と「NOR型」がありますが、この2つは、接続方法の違いによって、データの「書き込み方法」と「読み出し方法」が違うだけで、コアとなる「フラッシュメモリー」の原理は同じものです。

まずは、「フラッシュメモリー」の原理から説明していきたいと思います。

フラッシュメモリーの構造

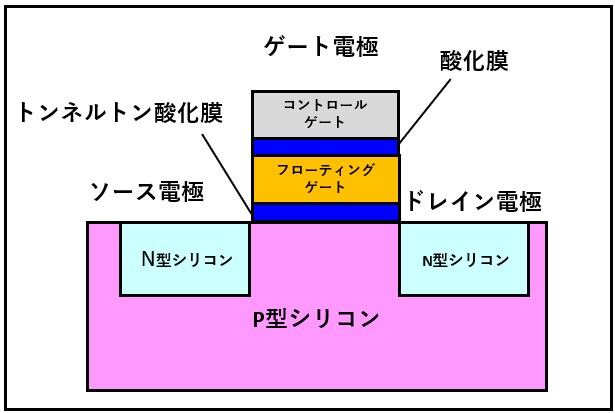

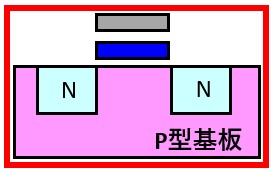

まずは、フラッシュメモリーの構造を下図に示します。基本的な原理は、「MOSトランジスタ」とよく似ています。

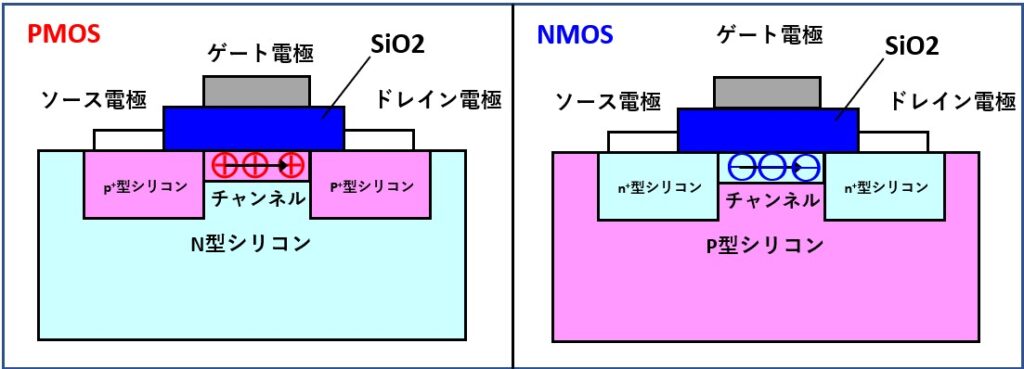

「MOSトランジスタ」の記事でも示した「MOSトランジスタ」の構造を示します。

大きな違いは2点あります。

①「MOSトランジスタ」がゲート電極だけだったのに対し、「フラッシュメモリー」では、ゲート電極が「コントロールゲート」と「フローティングゲート」の2層構造になっている点

②「MOSトランジスタ」には「PMOS」と「NMOS」の2種類があったのに対し、「フラッシュメモリー」では、「NMOS」一種類しかない点です。

メモリ機能の原理

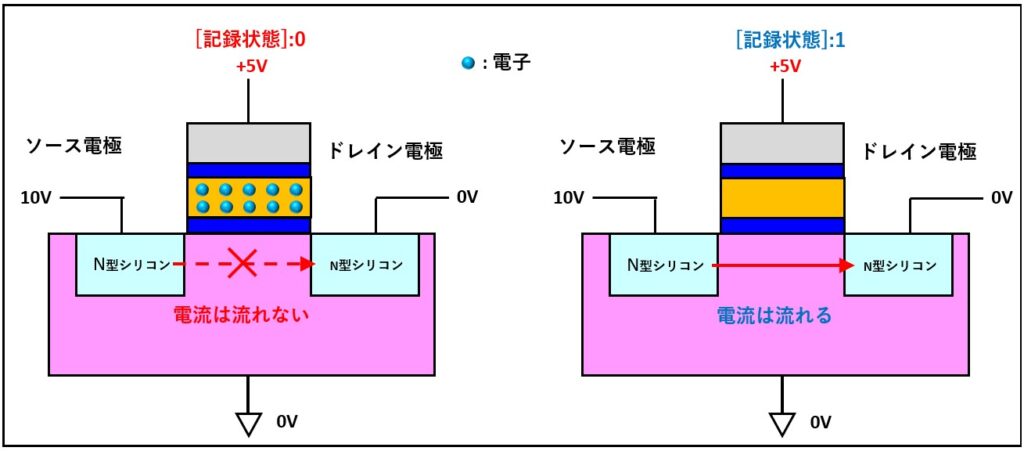

半導体のメモリなので、メモリということは「0」か「1」の状態を保持していなければなりません。ここでは、どうやってフラッシュメモリーが「0」と「1」を保持しているかを説明していこうと思います。

1.フラッシュメモリーの書き込み動作

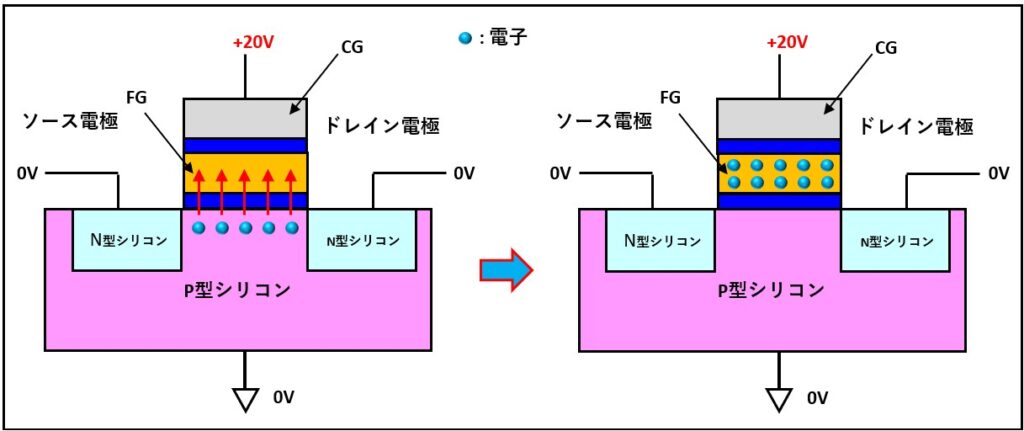

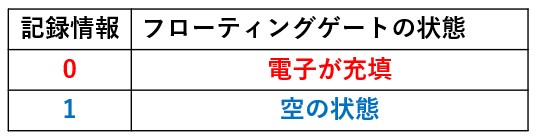

フラッシュメモリーの基本的な動作は、フローティング・ゲート(FG)と呼ばれる部分に電子(−電荷)を蓄えることで、記憶素子とします。

まず、記憶を保持する(書き込み動作)ですが、コントロール・ゲートに+20V程度をかけ、あとは、他の端子を0Vにすると、電子がトンネル酸化膜を貫通して、FGに流れ込みます。

この後、コントロール・ゲートにかけていた電圧を0Vにすると、書き込み動作は終了です。

2.フラッシュメモリーの読み出し動作

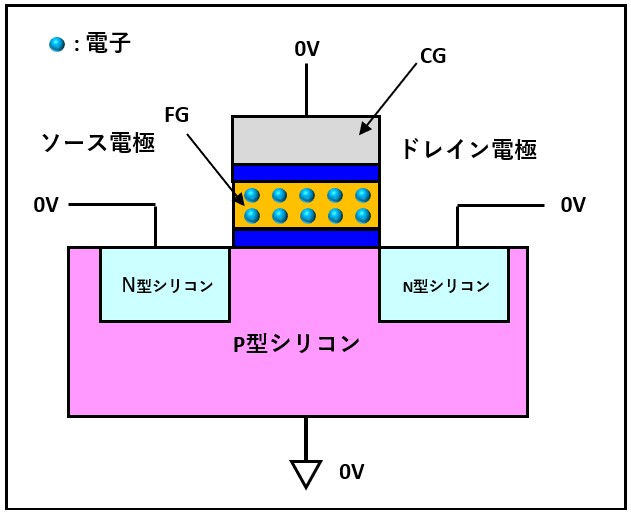

次に、フラッシュメモリーの読み出し動作を説明したいと思います。読み出し動作のためには、コントロール・ゲートに+5Vの電圧をかけてやります。

この時、フローティング・ゲートに電子が充填されている状態だと、その電子がコントロール・ゲートにかかった+5Vの効果を相殺してしまい、その下のP型シリコンには何の変化も起こらず、結果として「ソース」「ドレイン」間に電流が流れません。

また、フローティング・ゲートが空の状態だと、ゲート電圧を相殺する電子が存在しませんから、動作としては、普通のNMOSトランジスタとして働きます。結果として、「ソース」「ドレイン」間に電流がながれます。

この電流が「流れる」「流れない」で記憶状態を判断します。

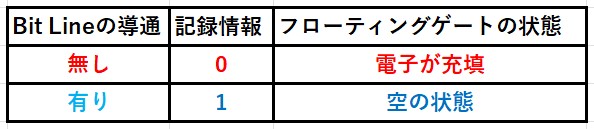

以下に、そのマトリックスを示します。

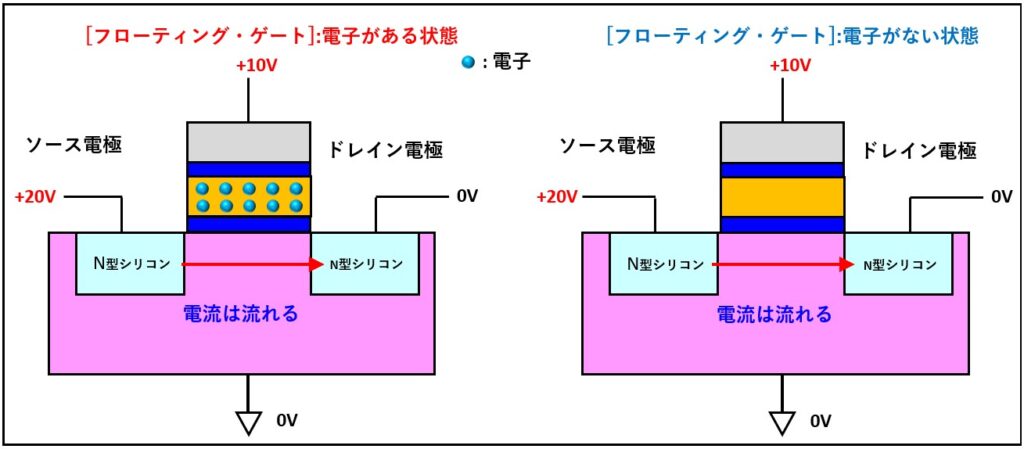

3.フラッシュメモリーの消去動作

次に、フラッシュメモリーの消去動作ですが、「書き込み動作」の逆作用を行います。

ゲート電極に0V状態にして、P型シリコンやソース電極に20Vの電圧をかけます。そうすると、フローティング・ゲートの中の電子はP型シリコンやソース電極に抜けて空になります。

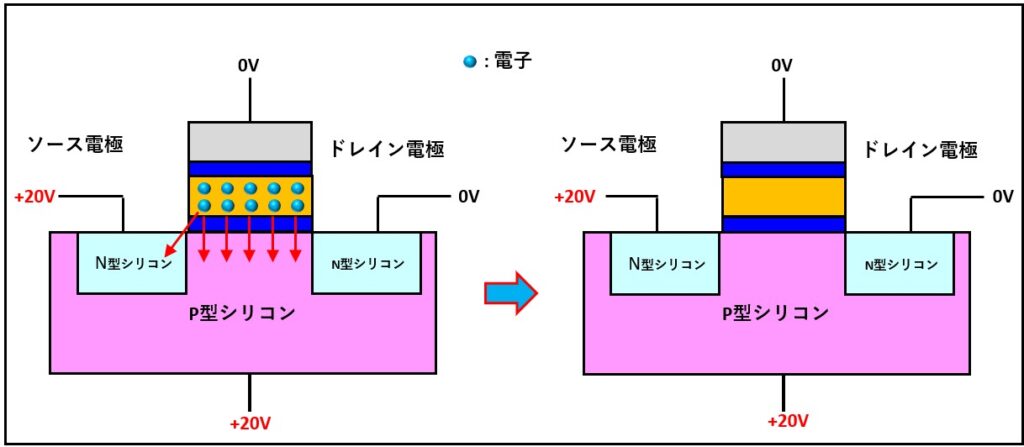

4.フラッシュメモリーのもう一つの動作

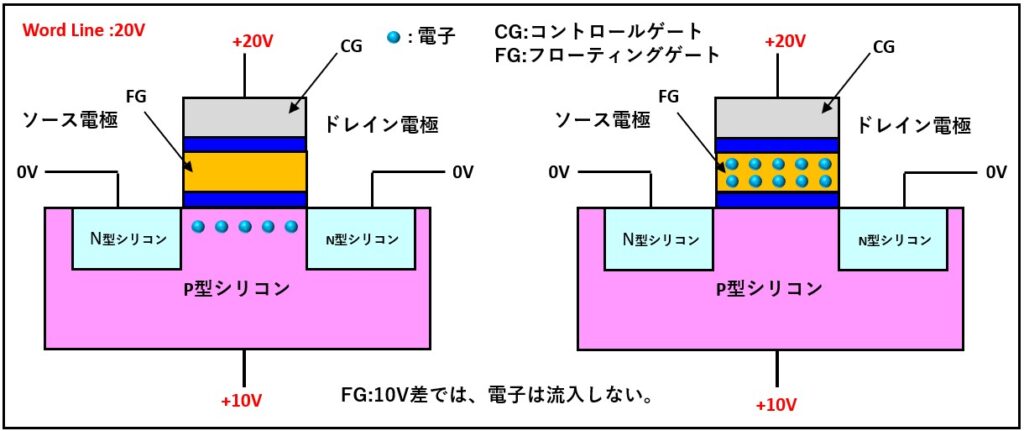

フラッシュメモリーには、もう一つの動作モードがあります。ゲート電極に+10Vをかけ、ソース電極に+20Vをかけると、この時ゲート-ソース間には実質的に+10Vの電圧がかかることになります。

これがどういう意味を持つのかは、NAND構造の説明時に、分かってもらえると思います。

なぜ「NAND」という名称なのか?

今までの記事の内容は、一つのメモリセルのメモリ機能の説明でした。「NANDフラッシュメモリー」とは、その一つ一つのメモリセルの接続方法に特徴があります。ここでは、なぜ「NAND」と名前になったのかを説明したいと思います。

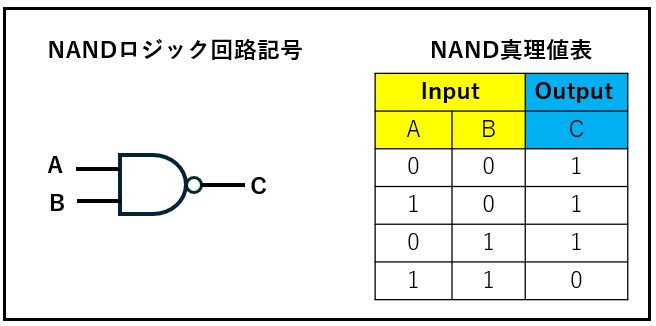

「NAND」というのは、論理回路の一つである「Not AND」を縮めて「NAND」と読んでいます。実際の論理回路の動作は、下記に記す「NAND真理値表」に従います。

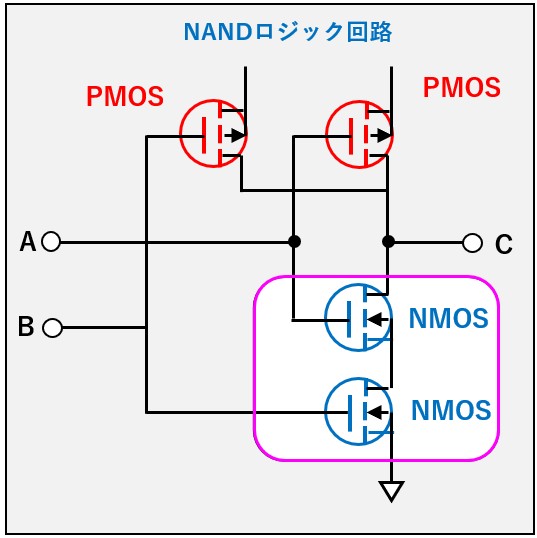

この真理値表を実際にMOSトランジスタで動作するように組んでみると下記のようになります。ここで注目してもらいたいのは、ピンク色の枠で囲った「NMOS」の接続形態です。「NMOS」が直列に接続されています。

後述しますが、「NANDフラッシュメモリー」は、NMOSが直列に連続に接続されているところが、「NANDロジック回路」に似ているために「NANDフラッシュメモリー」と呼ぶようになったようです。

ですので、「直列型フラッシュメモリー」という名前でもよかったと思います。

NANDフラッシュメモリーの構造

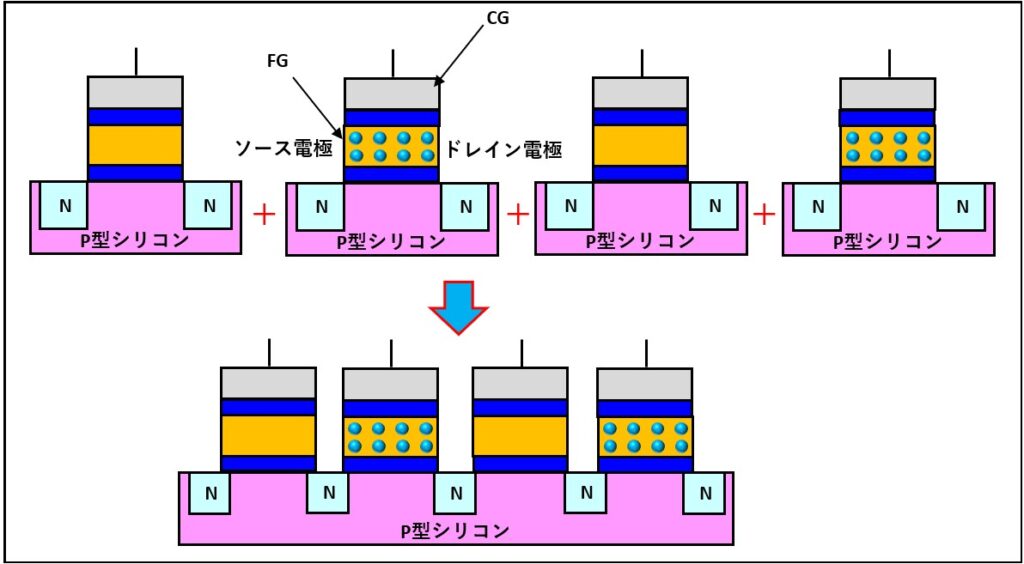

上記は、フラッシュメモリーの動作原理について説明してきました。NANDフラッシュメモリーは、その一つ一つのフラッシュメモリーの接続形態に特徴があります。

下記、フラッシュメモリー一つずつを直列に接続していきます。分かりやす様に、フラッシュメモリーは4つとします。この場合、となり指同士に「ソース電極」と「ドレイン電極」がならんでいますが、これを一つにまとめます。

こうすることによって、NANDフラッシュメモリーの特徴に一つである高密度化、高集積化が実現できます。

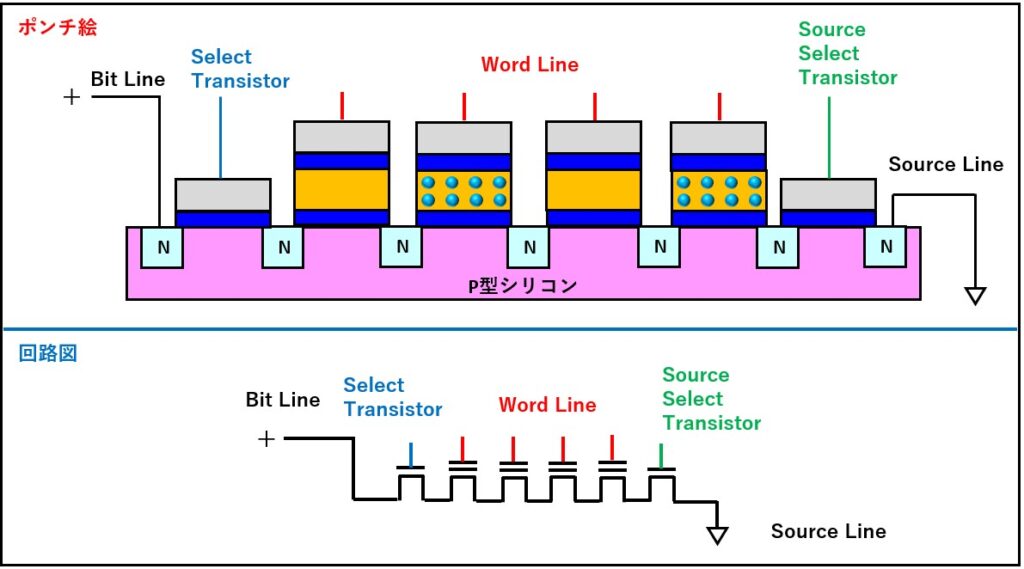

これだけでは、フラッシュメモリーを接続しただけですので、電源ラインを接続します。

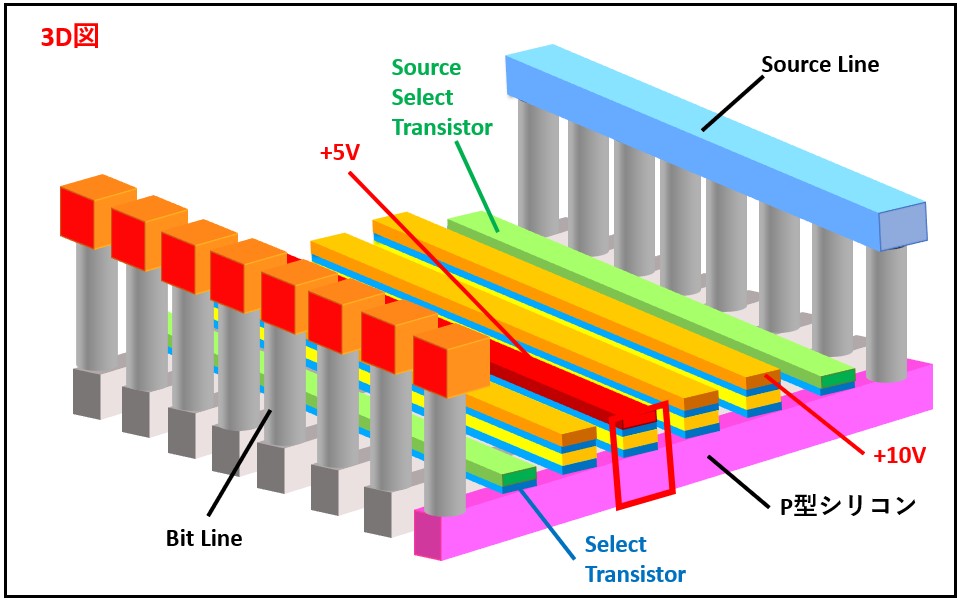

上記は、フラッシュメモリーの直列接続状態図だけだったので、説明としては一列だけにしましたが、それがNANDフラッシュメモリーの製品になるとその直列接続のラインが横(奥)に並んでが束になります。これによりさらに高集積化されることになります。

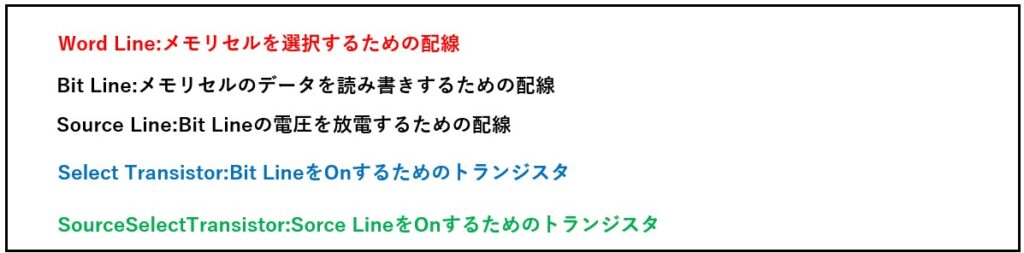

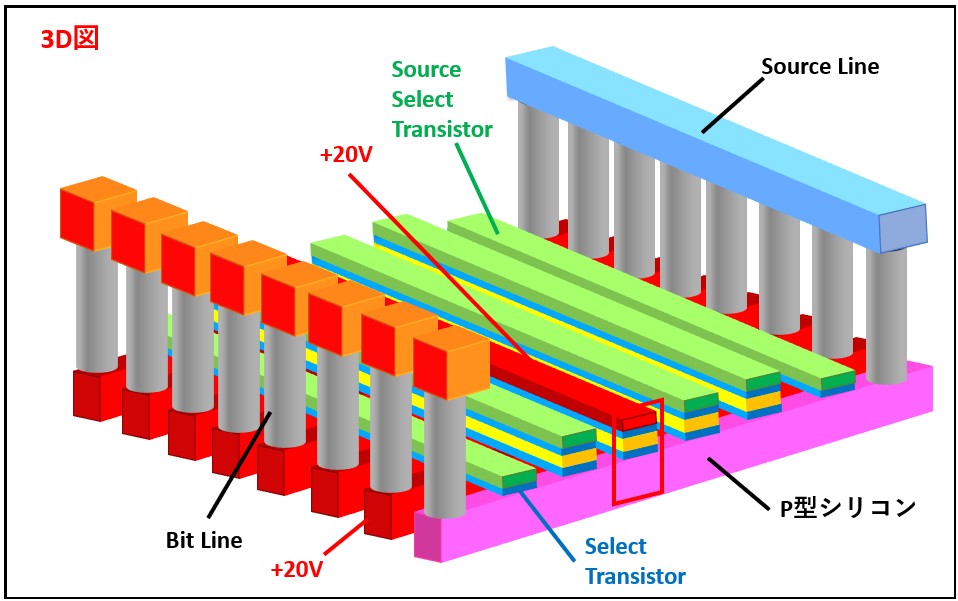

そのイメージを3Dで示したのが、下記の図になります。

NANDフラッシュメモリーのメモリー機能の原理

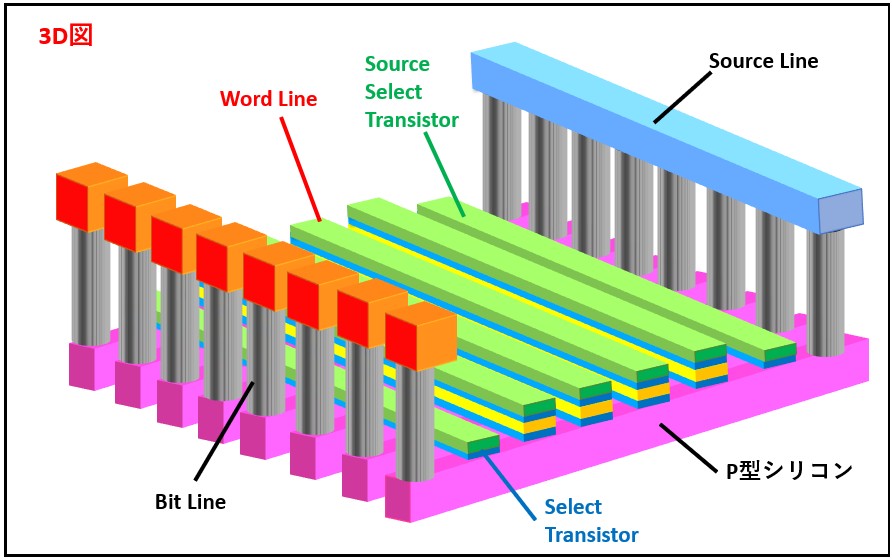

・NANDフラッシュメモリーの書き込み動作

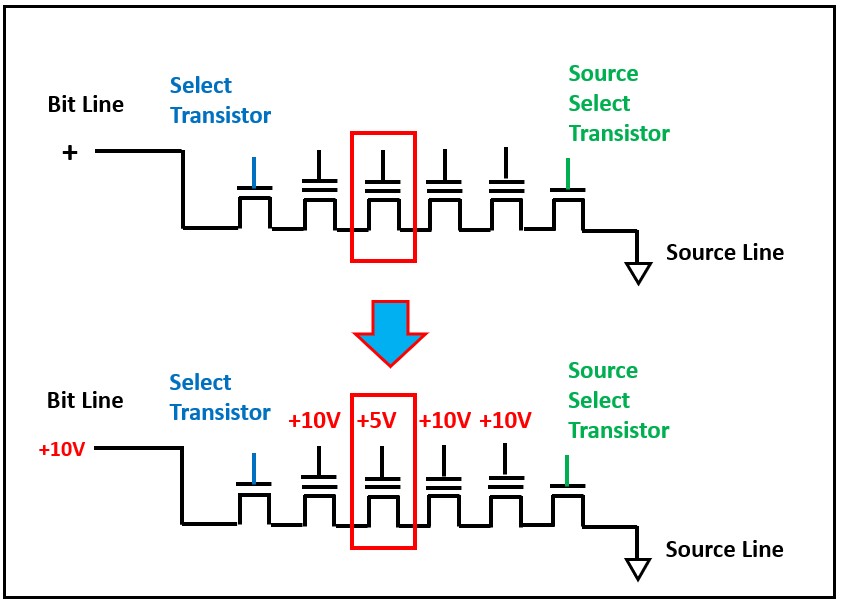

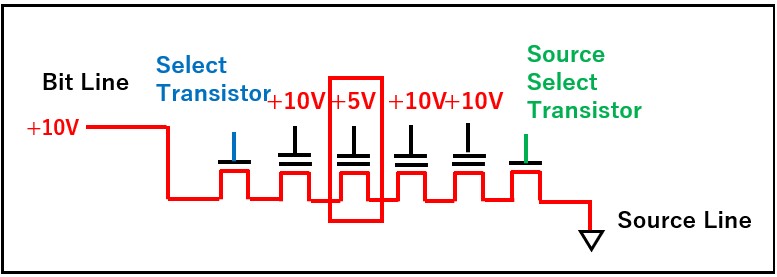

例えば、赤線で囲ったセルのフローティング・ゲートに電子を注入して、「0」にしたいとします。その時は、「1.フラッシュメモリーの書き込み動作」に従って、下側のP型シリコンを0Vにして、赤線で囲ったセルのワード線に20Vを印加してやれば、そのフローティング・ゲートに電子が注入されます。

しかし、注意しなければいけないのは、上図の「3D図」にあるように、ワード線は複数のP型シリコンの列にまたがっています。単に、一本のワード線だけを20Vにした場合は、そのワード線がまたがっているフローティング・ゲート全部に電子が注入されてしまう場合があります。

例えば、P型シリコンの一番手前の赤線で囲ったMOSセルのフローティング・ゲートだけに電子を注入したければ、該当するMOSセルのワードラインにだけ20Vを印加して、下図のように該当しないP型シリコン全部に10Vを印加してやります。

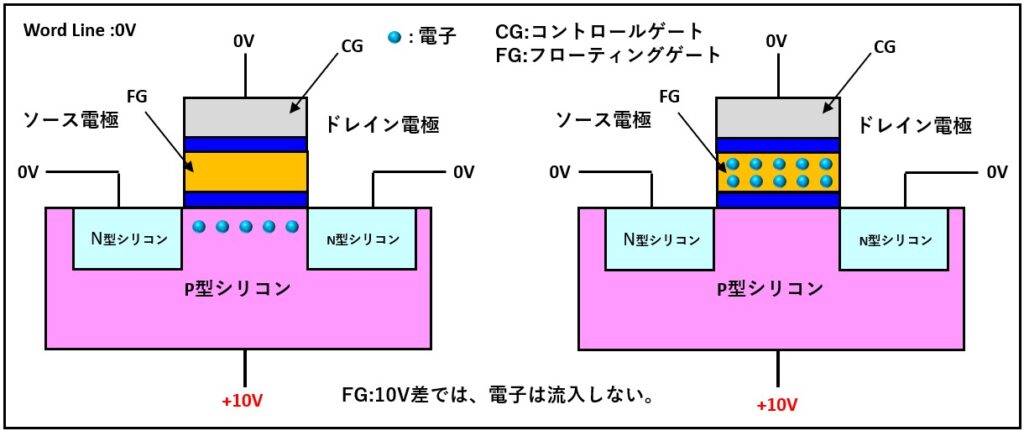

下図が、奥側の2本目以降のP型シリコン上のMOSセル電圧状態です。ワード線には20VとP型シリコンには10Vが印加されているので、フローティング・ゲートには10V電圧しかかっていない状態になります。10Vの電位差では、電子はフローティング・ゲートに移動しません。

結果として、フローティング・ゲートの状態は、電子が充填されていても、充填されていなくてもそのままの状態を保ち、赤線で囲ったセルのフローティング・ゲートにだけ電子が注入されることになります。

そして、下図が奥側の2本目以降で、ワード線に何も印加されていない、P型シリコン上のMOSセルにはやはり10Vしかかかっていない状態なので電子の移動はありません。

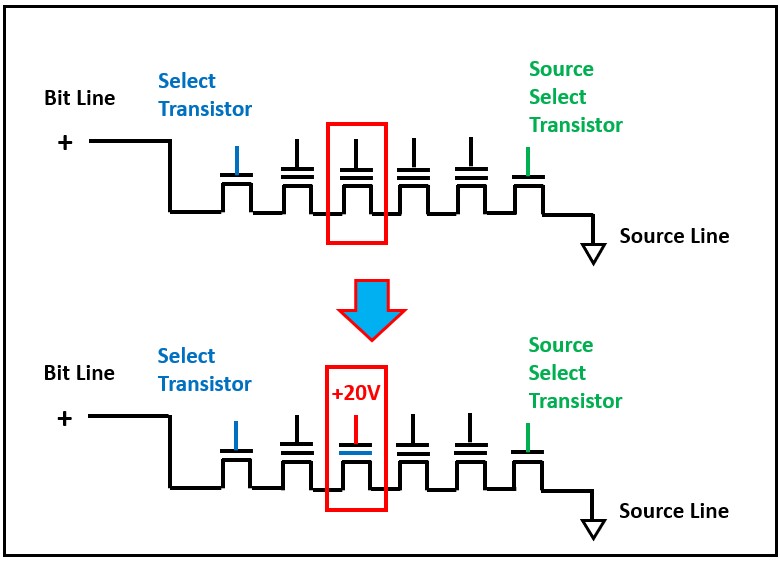

・NANDフラッシュメモリーの読み出し動作

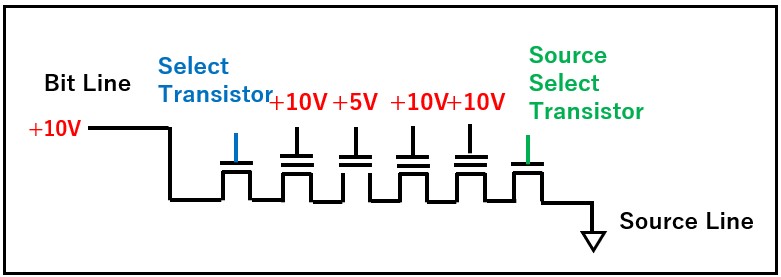

次に、NANDフラッシュメモリーの読み出し動作の説明をしたいと思います。読み出したいセルを赤く囲います。このセルが「0」か「1」を判別したいとします。

そして、それ以外にセルには、Word Lineに+10Vの電圧をかけます。ここで、「4.フラッシュメモリーのもう一つの動作」を参照して下さい。Word Lineに+10Vをかけると、そのセルはフローティングゲートに電子が入っていても、入っていなくてもどちらの状態でも自動的(強制的)にOn状態になります。

そして、判断対象となるセルが繋がっているBit Lineだけに+10V掛けます。他の判断対象にならないBit Lineは0V状態にします。

今回の例でいえば、1列目の左から2番目の赤枠で囲ったセルが判断対象になります。Bit Lineに+10Vの電圧がかけられているので、対象となったMOSセルがOnになっているか、Offになっているかで一番手前の電気回路の導通が変わってきます。

・NANDフラッシュメモリーの消去(削除)動作

コメント